## 3.3V 16K/32K x 36

## FLEx36™ Asynchronous Dual-Port Static RAM

#### **Features**

- True dual-ported memory cells which allow simultaneous access of the same memory location

- 16K x 36 organization (CY7C056V)

- 32K x 36 organization (CY7C057V)

- 0.25-micron CMOS for optimum speed/power

- · High-speed access: 12/15/20 ns

- · Low operating power

- Active: I<sub>CC</sub> = 250 mA (typical)

- Standby: I<sub>SB3</sub> = 10 μA (typical)

- Fully asynchronous operation

- Automatic power-down

- Expandable data bus to 72 bits or more using Master/Slave Chip Select when using more than one device

- On-Chip arbitration logic

- Semaphores included to permit software handshaking between ports

- · INT flag for port-to-port communication

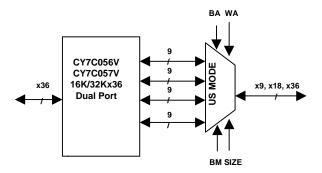

- Byte Select on Left Port

- Bus Matching on Right Port

- · Depth Expansion via dual chip enables

- Pin select for Master or Slave

- Commercial and Industrial Temperature Ranges

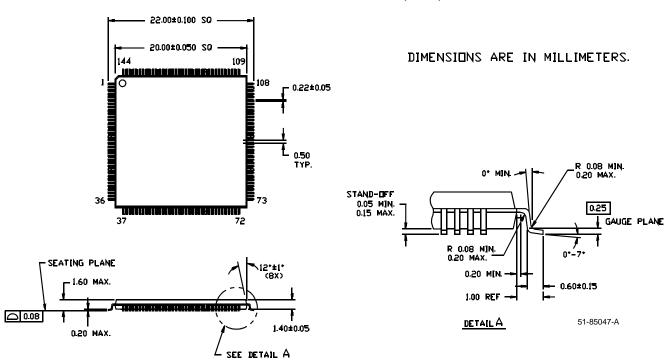

- Compact package

- -144-Pin TQFP (20 x 20 x 1.4 mm)

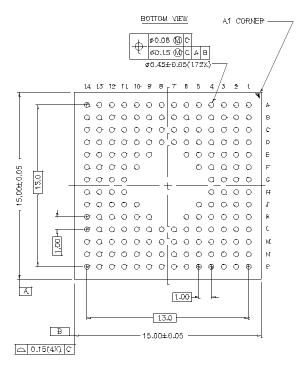

- -172-Ball BGA (1.0-mm pitch) (15 x 15 x.51 mm)

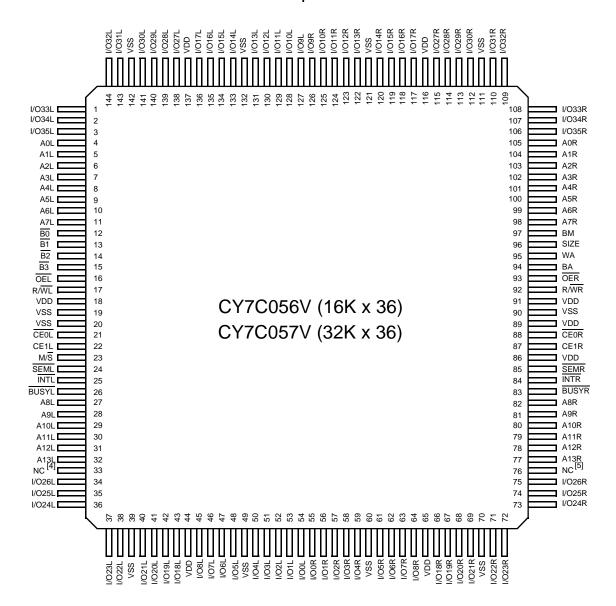

- $\underline{A_0-A_{13}}$  for 16K;  $A_0-A_{14}$  for 32K devices. BUSY is an output in Master mode and an input in Slave mode.

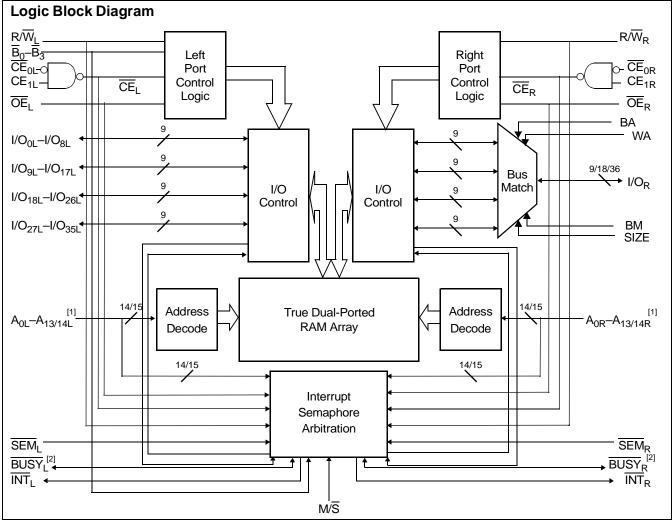

### **Functional Description**

The CY7C056V and CY7C057V are low-power CMOS 16K and 32K x 36 dual-port static RAMs. Various arbitration schemes are included on the devices to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The devices can be utilized as standalone 36-bit dual-port static RAMs or multiple devices can be combined in order to function as a 72-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 72-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory.

#### Note:

3.  $\overline{CE}$  is LOW when  $\overline{CE}_0 \le V_{IL}$  and  $CE_1 \ge V_{IH}$ .

Each port has independent control pins: Chip Enable  $(\overline{CE})^{[3]}$ , Read or Write Enable  $(R/\overline{W})$ , and Output Enable  $(\overline{OE})$ . Two flags are provided on each port  $(\overline{BUSY})$  and  $\overline{INT}$ . BUSY signals that the port is trying to access the same location currently being accessed by the other port. The Interrupt Flag  $(\overline{INT})$  permits communication between ports or systems by means of a mail box. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic Power-Down feature is controlled independently on each port by Chip Select  $(\overline{CE}_0)$  and  $\overline{CE}_1$  pins.

The CY7C056V and CY7C057V are available in 144-Pin Thin Quad Plastic Flatpack (TQFP) and 172-Ball Ball Grid Array (BGA) packages.

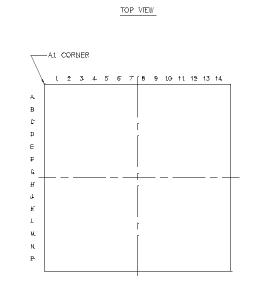

### **Pin Configurations**

### 144-Pin Thin Quad Flatpack (TQFP) **Top View**

- This pin is A14L for CY7C057V. This pin is A14R for CY7C057V.

### Pin Configurations (continued)

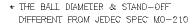

# 172-Ball Ball Grid Array (BGA) Top View

| _ | 1      | 2                 | 3      | 4      | 5      | 6      | 7      | 8      | 9      | 10     | 11     | 12     | 13                | 14     |

|---|--------|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------|--------|

| Α | I/O32L | I/O30L            | NC     | VSS    | I/O13L | VDD    | I/O11L | I/O11R | VDD    | I/O13R | VSS    | NC     | I/O30R            | I/O32R |

| В | A0L    | I/O33L            | I/O29  | I/O17L | I/O14L | I/O12L | I/O9L  | I/O9R  | I/O12R | I/O14R | I/O17R | I/O29R | I/O33R            | A0R    |

| С | NC     | A1L               | I/O31L | I/O27L | NC     | I/O15L | I/O10L | I/O10R | I/O15R | NC     | I/O27R | I/O31R | A1R               | NC     |

| D | A2L    | A3L               | I/O35L | I/O34L | I/O28L | I/O16L | VSS    | VSS    | I/O16R | I/O28R | I/O34R | I/O35R | A3R               | A2R    |

| E | A4L    | A5L               | NC     | B0L    | NC     | NC     |        |        | NC     | NC     | ВМ     | NC     | A5R               | A4R    |

| F | VDD    | A6L               | A7L    | B1L    | NC     |        | •      |        |        | NC     | SIZE   | A7R    | A6R               | VDD    |

| G | OEL    | B2L               | B3L    | CE0L   |        |        |        |        |        |        | CE0R   | ВА     | WA                | ŌER    |

| Н | VSS    | R/WL              | A8L    | CE1L   |        |        |        |        |        |        | CE1R   | A8R    | R/WR              | VSS    |

| J | A9L    | A10L              | VSS    | M/S    | NC     |        |        |        |        | NC     | VDD    | VDD    | A10R              | A9R    |

| K | A11L   | A12L              | NC     | SEML   | NC     | NC     |        |        | NC     | NC     | SEMR   | NC     | A12R              | A11R   |

| L | BUSYL  | A13L              | INTL   | I/O26L | I/O25L | I/O19L | VSS    | VSS    | I/O19R | I/O25R | I/O26R | ĪNTR   | A13R              | BUSYR  |

| М | NC     | NC <sup>[4]</sup> | I/O22L | I/O18L | NC     | I/O7L  | I/O2L  | I/O2R  | I/O7R  | NC     | I/O18R | I/O22R | NC <sup>[5]</sup> | NC     |

| N | I/O24L | I/O20L            | I/O8L  | I/O6L  | I/O5L  | I/O3L  | I/O0L  | I/00R  | I/O3R  | I/O5R  | I/O6R  | I/O8R  | I/O20R            | I/O24R |

| Р | I/O23L | I/O21L            | NC     | VSS    | I/O4L  | VDD    | I/O1L  | I/O1R  | VDD    | I/O4R  | VSS    | NC     | I/O21R            | I/O23R |

### **Selection Guide**

|                                                                           | CY7C056V<br>CY7C057V<br>-12 | CY7C056V<br>CY7C057V<br>-15 | CY7C056V<br>CY7C057V<br>-20 |

|---------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| Maximum Access Time (ns)                                                  | 12                          | 15                          | 20                          |

| Typical Operating Current (mA)                                            | 250                         | 240                         | 230                         |

| Typical Standby Current for I <sub>SB1</sub> (mA) (Both Ports TTL Level)  | 55                          | 50                          | 45                          |

| Typical Standby Current for I <sub>SB3</sub> (μA) (Both Ports CMOS Level) | 10 μΑ                       | 10 μΑ                       | 10 μΑ                       |

### **Pin Definitions**

| Left Port                             | Right Port                            | Description                                                                                                                   |

|---------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0L</sub> -A <sub>13/14L</sub>  | A <sub>0R</sub> -A <sub>13/14R</sub>  | Address (A <sub>0</sub> -A <sub>13</sub> for 16K; A <sub>0</sub> -A <sub>14</sub> for 32K devices)                            |

| SEML                                  | <u>SEM</u> <sub>R</sub>               | Semaphore Enable                                                                                                              |

| CE <sub>0L</sub> , CE <sub>1L</sub>   | CE <sub>0R</sub> , CE <sub>1R</sub>   | Chip Enable ( $\overline{CE}$ is LOW when $\overline{CE}_0 \le V_{IL}$ and $CE_1 \ge V_{IH}$ )                                |

| ĪNT <sub>L</sub>                      | ĪNT <sub>R</sub>                      | Interrupt Flag                                                                                                                |

| BUSYL                                 | BUSYR                                 | Busy Flag                                                                                                                     |

| I/O <sub>0L</sub> –I/O <sub>35L</sub> | I/O <sub>0R</sub> -I/O <sub>35R</sub> | Data Bus Input/Output                                                                                                         |

| ŌĒL                                   | <del>OE</del> <sub>R</sub>            | Output Enable                                                                                                                 |

| $R/\overline{W}_L$                    | R/W <sub>R</sub>                      | Read/Write Enable                                                                                                             |

| $\overline{B}_0 - \overline{B}_3$     |                                       | Byte Select Inputs. Asserting these signals enables read and write operations to the corresponding bytes of the memory array. |

|                                       | BM, SIZE                              | See Bus Matching for details.                                                                                                 |

|                                       | WA, BA                                | See Bus Matching for details.                                                                                                 |

| M/S                                   |                                       | Master or Slave Select                                                                                                        |

| V <sub>SS</sub>                       |                                       | Ground                                                                                                                        |

| V <sub>DD</sub>                       |                                       | Power                                                                                                                         |

### **Maximum Ratings**

| (Above which the useful life may be implines, not tested.) | paired. For user guide-                      |

|------------------------------------------------------------|----------------------------------------------|

| Storage Temperature                                        | 65°C to +150°C                               |

| Ambient Temperature with Power Applied                     | 55°C to +125°C                               |

| Supply Voltage to Ground Potential                         | –0.5V to +4.6V                               |

| DC Voltage Applied to Outputs in High Z State              | 0.5V to V <sub>DD</sub> +0.5V                |

| DC Input Voltage                                           | 0.5V to V <sub>DD</sub> +0.5V <sup>[6]</sup> |

### Note:

6. Pulse width < 20 ns.

| Output Current into Outputs (LOW) | 20 mA    |

|-----------------------------------|----------|

| Static Discharge Voltage          | . >2001V |

| Latch-Up Current                  | >200 mA  |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>DD</sub>                  |

|------------|------------------------|----------------------------------|

| Commercial | 0°C to +70°C           | $3.3\text{V} \pm 165 \text{ mV}$ |

| Industrial | –40°C to +85°C         | $3.3\text{V} \pm 165 \text{ mV}$ |

Shaded areas contain advance information.

### Electrical Characteristics Over the Operating Range [7, 8]

|                  |                                                                            |            |      |      |      | _    | 77C05 |      |      |      |      |      |

|------------------|----------------------------------------------------------------------------|------------|------|------|------|------|-------|------|------|------|------|------|

|                  |                                                                            |            |      | -12  |      |      | -15   |      |      | -20  |      |      |

| Parameter        | Description                                                                |            | Min. | Typ. | Мах. | Min. | Typ.  | Мах. | Min. | Typ. | Мах. | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage<br>(V <sub>DD</sub> = Min., I <sub>OH</sub> = -4.0 mA) |            | 2.4  |      |      | 2.4  |       |      | 2.4  |      |      | V    |

| V <sub>OL</sub>  | Output LOW Voltage<br>(V <sub>DD</sub> = Min., I <sub>OL</sub> = +4.0 mA)  |            |      |      | 0.4  |      |       | 0.4  |      |      | 0.4  | ٧    |

| V <sub>IH</sub>  | Input HIGH Voltage                                                         |            | 2.0  |      |      | 2.0  |       |      | 2.0  |      |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                                          |            |      | 0.8  |      |      | 0.8   |      |      | 0.8  | V    |      |

| I <sub>OZ</sub>  | Output Leakage Current                                                     |            | -10  |      | 10   | -10  |       | 10   | -10  |      | 10   | μΑ   |

| I <sub>CC</sub>  | Operating Current (V <sub>DD</sub> = Max.,                                 | Commercial |      | 250  | 385  |      | 240   | 360  |      | 230  | 340  | mΑ   |

|                  | I <sub>OUT</sub> = 0 mA) Outputs Disabled                                  | Industrial |      |      |      |      | 265   | 385  |      |      |      | mA   |

| I <sub>SB1</sub> | Standby Current (Both Ports TTL                                            | Commercial |      | 55   | 75   |      | 50    | 70   |      | 45   | 65   | mA   |

|                  | Level and Deselected) $f = f_{MAX}$                                        | Industrial |      |      |      |      | 65    | 95   |      |      |      | mA   |

| I <sub>SB2</sub> | Standby Current (One Port TTL                                              | Commercial |      | 180  | 240  |      | 175   | 230  |      | 165  | 210  | mA   |

|                  | Level and Deselected) $f = f_{MAX}$                                        | Industrial |      |      |      |      | 190   | 255  |      |      |      | mA   |

| I <sub>SB3</sub> | Standby Current (Both Ports CMOS                                           | Commercial |      | 0.01 | 1    |      | 0.01  | 1    |      | 0.01 | 1    | mΑ   |

|                  | Level and Deselected) f =0                                                 | Industrial |      |      |      |      | 0.01  | 1    |      |      |      | mA   |

| I <sub>SB4</sub> | Standby Current (One Port CMOS                                             | Commercial |      | 160  | 210  | 1    | 155   | 200  |      | 145  | 180  | mA   |

|                  | Level and Deselected) f = f <sub>MAX</sub> <sup>[9]</sup>                  | Industrial |      |      |      |      | 170   | 215  |      |      |      | mA   |

### Capacitance<sup>[10]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{DD} = 3.3V$                         | 10   | pF   |

Cross Levels are V<sub>DD</sub> − 0.2V≤ V<sub>Z≤</sub>0.2V.

Deselection for a port occurs if CE<sub>0</sub> is HIGH or if CE<sub>1</sub> is LOW.

f<sub>MAX</sub> = 1/t<sub>RC</sub> = All inputs cycling at f = 1/t<sub>RC</sub> (except Output Enable). f = 0 means no address or control lines change. This applies only to inputs at CMOS level standby I<sub>SB3</sub>.

Tested initially and after any design or process changes that may affect these parameters.

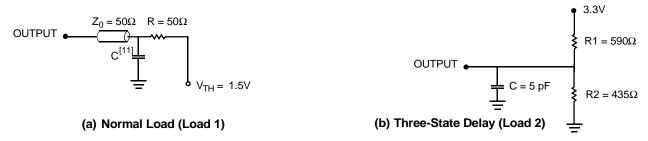

### **AC Test Load and Waveforms**

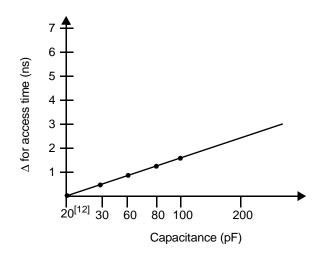

### (b) Load Derating Curve

#### Notes:

External AC Test Load Capacitance = 10 pF.

(Internal I/O pad Capacitance = 10 pF) + AC Test Load.

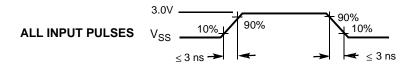

### Switching Characteristics Over the Operating Range<sup>[13]</sup>

|                                    |                                     |      |      |      | 056V<br>057V |      |      |      |

|------------------------------------|-------------------------------------|------|------|------|--------------|------|------|------|

|                                    |                                     |      | 12   |      | 15           | -2   | 20   |      |

| Parameter                          | Description                         | Min. | Max. | Min. | Max.         | Min. | Max. | Unit |

| Read Cycle                         |                                     |      | •    |      | •            |      |      |      |

| t <sub>RC</sub>                    | Read Cycle Time                     | 12   |      | 15   |              | 20   |      | ns   |

| t <sub>AA</sub>                    | Address to Data Valid               |      | 12   |      | 15           |      | 20   | ns   |

| t <sub>OHA</sub>                   | Output Hold From Address Change     | 3    |      | 3    |              | 3    |      | ns   |

| t <sub>ACE</sub> [3, 14]           | CE LOW to Data Valid                |      | 12   |      | 15           |      | 20   | ns   |

| t <sub>DOE</sub>                   | OE LOW to Data Valid                |      | 8    |      | 10           |      | 12   | ns   |

| t <sub>LZOE</sub> [3, 15, 16, 17]  | OE Low to Low Z                     | 0    |      | 0    |              | 0    |      | ns   |

| t <sub>HZOF</sub> [3, 15, 16, 17]  | OE HIGH to High Z                   |      | 10   |      | 10           |      | 12   | ns   |

| t <sub>LZCE</sub> [3, 13, 16, 17]  | CE LOW to Low Z                     | 3    |      | 3    |              | 3    |      | ns   |

| t <sub>HZCE</sub> [3, 15, 16, 17]  | CE HIGH to High Z                   |      | 10   |      | 10           |      | 12   | ns   |

| t <sub>LZBE</sub>                  | Byte Enable to Low Z                | 3    |      | 3    |              | 3    |      | ns   |

| t <sub>HZBE</sub>                  | Byte Enable to High Z               |      | 10   |      | 10           |      | 12   | ns   |

| t <sub>PU</sub> <sup>[3, 17]</sup> | CE LOW to Power-Up                  | 0    |      | 0    |              | 0    |      | ns   |

| t <sub>PD</sub> <sup>[3, 17]</sup> | CE HIGH to Power-Down               |      | 12   |      | 15           |      | 20   | ns   |

| t <sub>ABE</sub> <sup>[14]</sup>   | Byte Enable Access Time             |      | 12   |      | 15           |      | 20   | ns   |

| Write Cycle                        |                                     |      | 1    | ı    | 1            | ı    |      |      |

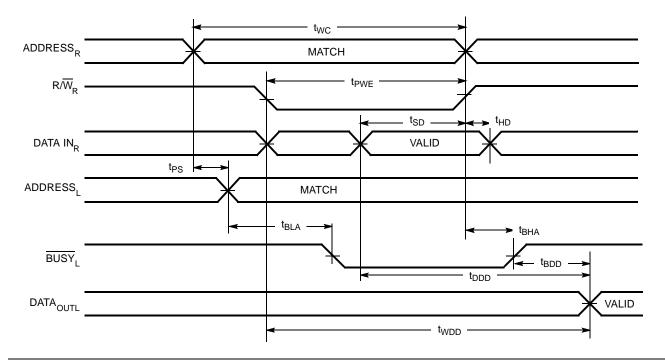

| t <sub>WC</sub>                    | Write Cycle Time                    | 12   |      | 15   |              | 20   |      | ns   |

| t <sub>SCE</sub> [3, 14]           | CE LOW to Write End                 | 10   |      | 12   |              | 15   |      | ns   |

| t <sub>AW</sub>                    | Address Valid to Write End          | 10   |      | 12   |              | 15   |      | ns   |

| t <sub>HA</sub>                    | Address Hold From Write End         | 0    |      | 0    |              | 0    |      | ns   |

| t <sub>SA</sub> <sup>[14]</sup>    | Address Set-Up to Write Start       | 0    |      | 0    |              | 0    |      | ns   |

| t <sub>PWE</sub>                   | Write Pulse Width                   | 10   |      | 12   |              | 15   |      | ns   |

| t <sub>SD</sub>                    | Data Set-Up to Write End            | 10   |      | 10   |              | 15   |      | ns   |

| t <sub>HD</sub>                    | Data Hold From Write End            | 0    |      | 0    |              | 0    |      | ns   |

| t <sub>HZWE</sub> [16, 17]         | $R/\overline{W}$ LOW to High Z      |      | 10   |      | 10           |      | 12   | ns   |

| t <sub>LZWE</sub> [16, 17]         | R/W HIGH to Low Z                   | 3    |      | 3    |              | 3    |      | ns   |

| t <sub>WDD</sub> <sup>[18]</sup>   | Write Pulse to Data Delay           |      | 25   |      | 30           |      | 45   | ns   |

| t <sub>DDD</sub> <sup>[18]</sup>   | Write Data Valid to Read Data Valid | 1    | 20   |      | 25           |      | 30   | ns   |

- Notes:

13. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified lovely and 10-pF load capacitance.

14. To access RAM, \(\overline{CE} = L\) and \(\overline{SEM} = H\). To access semaphore, \(\overline{CE} = H\) and \(\overline{SEM} = L\). Either condition must be valid for the entire t<sub>SCE</sub> time.

15. At any given temperature and voltage condition for any given device, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> and t<sub>HZCE</sub> is less than t<sub>LZCE</sub>.

16. Test conditions used are Load 2.

17. This parameter is guaranteed by design, but it is not production tested. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.

18. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.

## $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range}^{[13]} \, (\text{continued})$

|                            |                                 |      | CY7C056V<br>CY7C057V |      |      |      |      |      |

|----------------------------|---------------------------------|------|----------------------|------|------|------|------|------|

|                            |                                 |      | -12 -15 -20          |      | 20   |      |      |      |

| Parameter                  | Description                     | Min. | Max.                 | Min. | Max. | Min. | Max. | Unit |

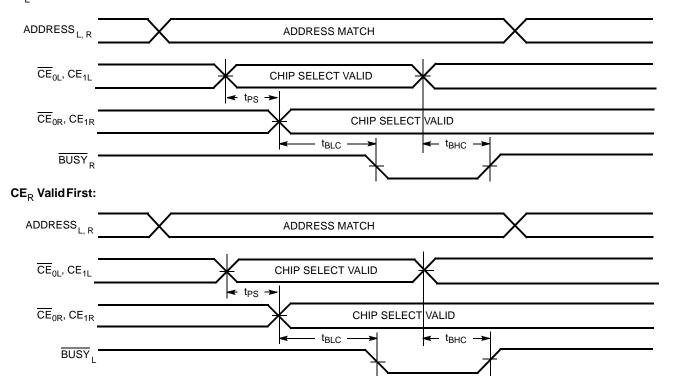

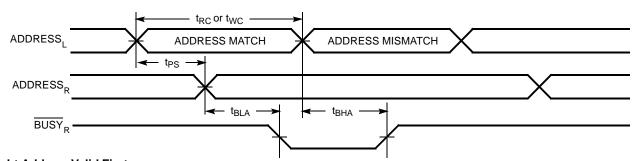

| Busy Timing <sup>[1]</sup> | 9]                              |      | •                    |      | •    |      |      |      |

| t <sub>BLA</sub>           | BUSY LOW from Address Match     |      | 12                   |      | 15   |      | 20   | ns   |

| t <sub>BHA</sub>           | BUSY HIGH from Address Mismatch |      | 12                   |      | 15   |      | 20   | ns   |

| t <sub>BLC</sub>           | BUSY LOW from CE LOW            |      | 12                   |      | 15   |      | 20   | ns   |

<sup>19.</sup> Test conditions used are Load 1.

### Switching Characteristics Over the Operating Range<sup>[13]</sup> (continued)

|                                  |                                   | -12 -15 -20 |      | 20   |      |      |      |      |

|----------------------------------|-----------------------------------|-------------|------|------|------|------|------|------|

| Parameter                        | Description                       | Min.        | Max. | Min. | Max. | Min. | Max. | Unit |

| Busy Timing <sup>[1</sup>        | 9]                                |             | •    |      | •    |      | •    |      |

| t <sub>BHC</sub>                 | BUSY HIGH from CE HIGH            |             | 12   |      | 15   |      | 20   | ns   |

| t <sub>PS</sub>                  | Port Set-Up for Priority          | 5           |      | 5    |      | 5    |      | ns   |

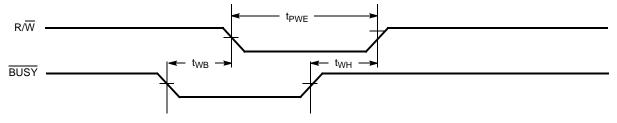

| t <sub>WB</sub>                  | R/W LOW after BUSY (Slave)        | 0           |      | 0    |      | 0    |      | ns   |

| t <sub>WH</sub>                  | R/W HIGH after BUSY HIGH (Slave)  | 11          |      | 13   |      | 15   |      | ns   |

| t <sub>BDD</sub> <sup>[20]</sup> | BUSY HIGH to Data Valid           |             | 12   |      | 15   |      | 20   | ns   |

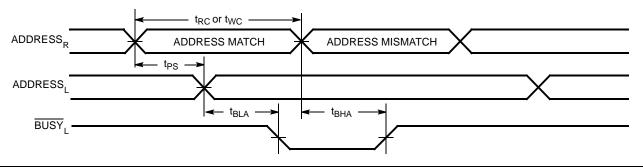

| Interrupt Timi                   | ng <sup>[19]</sup>                |             |      |      |      |      |      |      |

| t <sub>INS</sub>                 | INT Set Time                      |             | 12   |      | 15   |      | 20   | ns   |

| t <sub>INR</sub>                 | INT Reset Time                    |             | 12   |      | 15   |      | 20   | ns   |

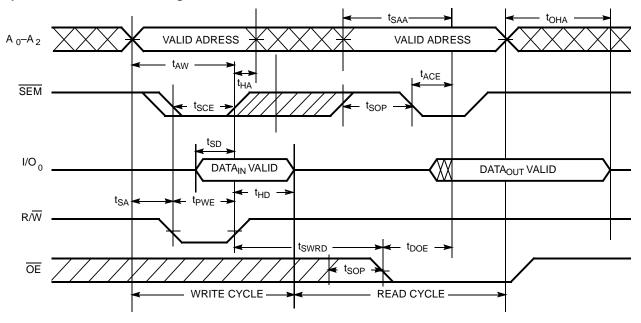

| Semaphore Ti                     | ming                              |             | •    |      |      |      |      |      |

| t <sub>SOP</sub>                 | SEM Flag Update Pulse (OE or SEM) | 10          |      | 10   |      | 10   |      | ns   |

| t <sub>SWRD</sub>                | SEM Flag Write to Read Time       | 5           |      | 5    |      | 5    |      | ns   |

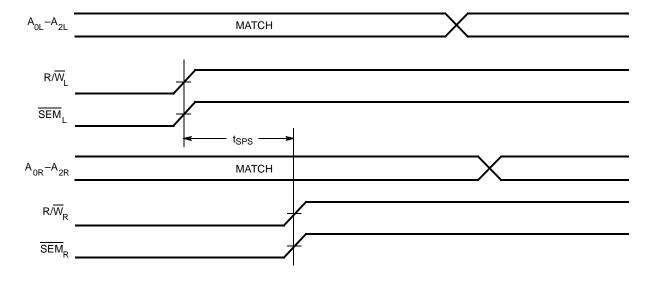

| t <sub>SPS</sub>                 | SEM Flag Contention Window        | 5           |      | 5    |      | 5    |      | ns   |

| t <sub>SAA</sub>                 | SEM Address Access Time           |             | 12   |      | 15   |      | 20   | ns   |

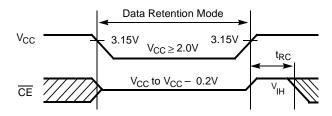

### **Data Retention Mode**

The CY7C056V and CY7C057V are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:

- 1. Chip Enable  $(\overline{CE})^{[3]}$  must be held HIGH during data retention, within  $V_{DD}$  to  $\dot{V}_{DD} - 0.2V$ .

- 2.  $\overline{\text{CE}}$  must be kept between V<sub>DD</sub> 0.2V and 70% of V<sub>DD</sub> during the power-up and power-down transitions.

- 3. The RAM can begin operation >t $_{RC}$  after  $V_{DD}$  reaches the minimum operating voltage (3.15 volts).

### **Timing**

| Parameter          | Test Conditions <sup>[21]</sup> | Max. | Unit |

|--------------------|---------------------------------|------|------|

| ICC <sub>DR1</sub> | @ VDD <sub>DR</sub> = 2V        | 50   | μΑ   |

- 20. t<sub>BDD</sub> is a calculated parameter and is the greater of t<sub>WDD</sub>-t<sub>PWE</sub> (actual) or t<sub>DDD</sub>-t<sub>SD</sub> (actual).

21. CE = V<sub>DD</sub>, V<sub>in</sub> = V<sub>SS</sub> to V<sub>DD</sub>, T<sub>A</sub> = 25°C. This parameter is guaranteed but not tested.

### **Switching Waveforms**

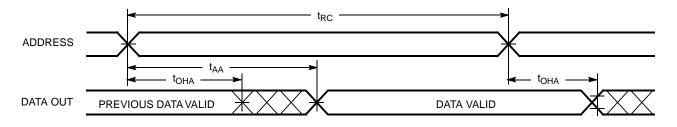

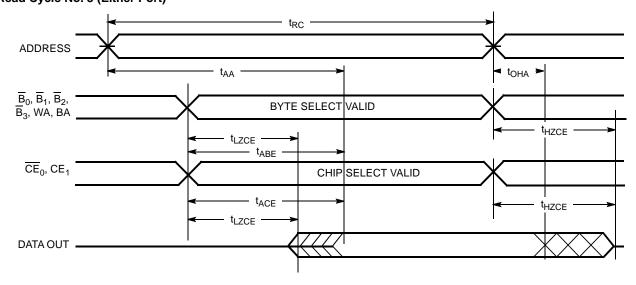

### Read Cycle No. 1 (Either Port Address Access) [22, 23, 24]

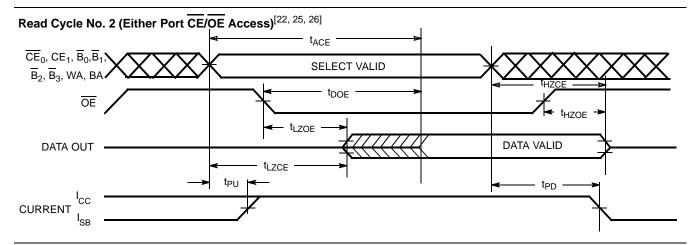

### Read Cycle No. 3 (Either Port) [22, 24, 25, 26]

- 22. R/W is HIGH for read cycles.

23. Device is continuously selected. CE<sub>0</sub> = V<sub>IL</sub>, CE<sub>1</sub>=V<sub>IH</sub>, and B

0, B

1, B

2, B

3, WA, BA are valid. This waveform cannot be used for semaphore reads.

- 24.  $\overline{OE} = V_{IL}$ .

25. Address valid prior to or coinciding with  $\overline{CE}_0$  transition LOW and  $\overline{CE}_1$  transition HIGH.

26. To access RAM,  $\overline{CE}_0 = V_{IL}$ ,  $\overline{CE}_1 = V_{IH}$ ,  $\overline{B}_0$ ,  $\overline{B}_1$ ,  $\overline{B}_2$ ,  $\overline{B}_3$ , WA, BA are valid, and  $\overline{SEM} = V_{IH}$ . To access semaphore,  $\overline{CE}_0 = V_{IH}$ ,  $\overline{CE}_1 = V_{IL}$  and  $\overline{SEM} = V_{IL}$  or  $\overline{CE}_0$  and  $\overline{SEM} = V_{IL}$ , and  $\overline{CE}_1 = \overline{B}_2 = \overline{B}_3$ ,  $\overline{E}_1 = \overline{B}_3 = \overline{B}_$

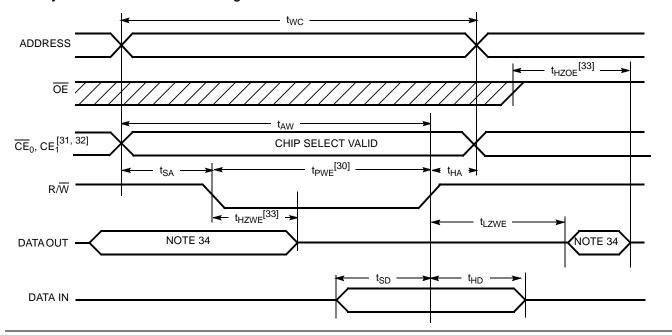

### Write Cycle No. 1: R/W Controlled Timing [27, 28, 29, 30]

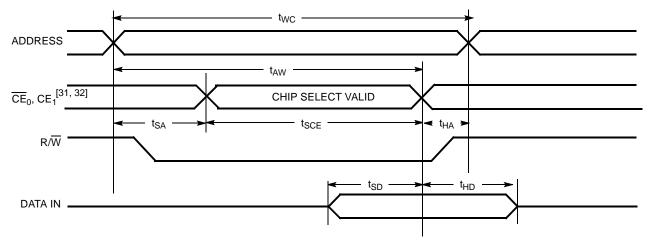

### Write Cycle No. 2: CE Controlled Timing<sup>[27, 28, 29, 35]</sup>

- Notes:

R/W must be HIGH during all address transitions.

A write occurs during the overlap (t<sub>SCE</sub> or t<sub>PWE</sub>) of CE<sub>0</sub>=V<sub>IL</sub> and CE₁=V<sub>IH</sub> or SEM=V<sub>IL</sub> and B̄<sub>0-3</sub> LOW.

thub is measured from the earlier of CE₀/CE₁ or R/W or (SEM or R/W) going HIGH at the end of Write Cycle.

If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of t<sub>PWE</sub> or (t<sub>HZWE</sub> + t<sub>SD</sub>) to allow the I/O drivers to turn off and data to be placed on the bus for the required t<sub>SD</sub>. If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified t<sub>PWE</sub>.

To access RAM, CE₀ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₀, CE₀ = V<sub>IL</sub>, B₀ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₁, CE₀ = V<sub>IL</sub>, B₁ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₂, CE₀ = V<sub>IL</sub>, B₂ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₃, CE₀ = V<sub>IL</sub>, B₃ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₃, CE₀ = V<sub>IL</sub>, B₃ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

To access byte B₃, CE₀ = V<sub>IL</sub>, B₃ = V<sub>IL</sub>, CE₁=SEM = V<sub>IH</sub>.

Transition is measured ±150 mV from steady state with a 5-pF load (including scope and jig). This parameter is sampled and not 100% tested.

During this period, the I/O pins are in the output state, and input signals must not be applied.

If the CE₀ LOW and CE₁ HIGH or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance state.

### Semaphore Read After Write Timing, Either Side<sup>[36]</sup>

### Timing Diagram of Semaphore Contention<sup>[37, 38, 39]</sup>

- 36.  $\overline{CE}_0$  = HIGH and  $CE_1$  = LOW for the duration of the above timing (both write and read cycle).

- 37. I/O<sub>0R</sub> = I/O<sub>0L</sub> = LOW (request semaphore); \( \overline{CE}\_{0R} = \overline{CE}\_{0L} = HIGH \) and \( \overline{CE}\_{1R} = CE\_{1L} = LOW. \)

38. Semaphores are reset (available to both ports) at cycle start.

39. If t<sub>SPS</sub> is violated, the semaphore will definitely be obtained by one side or the other, but which side will get the semaphore is unpredictable.

### Timing Diagram of Write with BUSY (M/S=HIGH)[40]

### Write Timing with Busy Input (M/S=LOW)

Note: 40.  $\overline{CE}_{0L} = \overline{CE}_{0R} = LOW$ ;  $CE_{1L} = CE_{1R} = HIGH$ .

# <u>Bu</u>sy Timing Diagram No. 1 ( $\overline{\text{CE}}$ Arbitration)<sup>[41]</sup> CE<sub>L</sub>Valid First:

## Busy Timing Diagram No. 2 (Address Arbitration)<sup>[41]</sup> Left Address Valid First:

### Right Address Valid First:

<sup>41.</sup> If t<sub>PS</sub> is violated, the busy signal will be asserted on one side or the other, but there is no guarantee to which side BUSY will be asserted.

<sup>42.</sup>  $t_{HA}$  depends on which enable pin  $(\overline{CE}_{0L}/CE_{1L} \text{ or } R.\overline{W}_L)$  is deasserted first.

43.  $t_{INS}$  or  $t_{INR}$  depends on which enable pin  $(\overline{CE}_{0L}/CE_{1L} \text{ or } R.\overline{W}_L)$  is asserted last.

#### **Architecture**

The CY7C056V and CY7C057V consist of an array of 16K and 32K words of 36 bits each of dual-port RAM cells, I/O and address lines, and control signals ( $\overline{\text{CE}_0}/\text{CE}_1$ ,  $\overline{\text{OE}}$ ,  $\overline{\text{R/W}}$ ). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes/reads to the same location, a BUSY pin is provided on each port. Two Interrupt ( $\overline{\text{INT}}$ ) pins can be utilized for port-to-port communication. Two Semaphore ( $\overline{\text{SEM}}$ ) control pins are used for allocating shared resources. With the M/S pin, the devices can function as a master ( $\overline{\text{BUSY}}$  pins are outputs) or as a slave ( $\overline{\text{BUSY}}$  pins are inputs). The devices also have an automatic power-down feature controlled by  $\overline{\text{CE}_0}/\overline{\text{CE}_1}$ . Each port is provided with its own Output Enable control ( $\overline{\text{OE}}$ ), which allows data to be read from the device.

### **Functional Description**

#### **Write Operation**

Data must be set up for a duration of  $t_{SD}$  before the rising edge of  $R\overline{W}$  in order to guarantee a valid write. A write operation is controlled by either the  $R\overline{W}$  pin (see Write Cycle No. 1 waveform) or the  $\overline{CE}_0$  and  $CE_1$  pins (see Write Cycle No. 2 waveform). Required inputs for non-contention operations are summarized in *Table 1*.

If a location is being written to by one port and the opposite port attempts to read that location, a port-to-port flowthrough delay must occur before the data is read on the output; otherwise the data read is not deterministic. Data will be valid on the port t<sub>DDD</sub> after the data is presented on the other port.

#### **Read Operation**

When reading the device, the user must assert both the  $\underline{OE}$  and  $\overline{CE}^{[3]}$  pins. Data will be available  $t_{ACE}$  after  $\overline{CE}$  or  $t_{DOE}$  after  $\overline{OE}$  is asserted. If the user wishes to access a semaphore flag, then the  $\overline{SEM}$  pin must be asserted instead of the  $\overline{CE}^{[3]}$  pin, and  $\overline{OE}$  must also be asserted.

### Interrupts

The upper two memory locations may be used for message passing. The highest memory location (3FFF for the CY7C056V, 7FFF for the CY7C057V) is the mailbox for the right port and the second-highest memory location (3FFE for the CY7C056V, 7FFE for the CY7C057V) is the mailbox for the left port. When one port writes to the other port's mailbox, an interrupt is generated to the owner. The interrupt is reset when the owner reads the contents of the mailbox. The message is user defined.

Each port can read the other port's mailbox without resetting the interrupt. The active state of the busy signal (to a port) prevents the port from setting the interrupt to the winning port. Also, an active busy to a port prevents that port from reading its own mailbox and, thus, resetting the interrupt to it.

If an application does not require message passing, do not connect the interrupt pin to the processor's interrupt request input pin.

The operation of the interrupts and their interaction with Busy are summarized in *Table 2*.

#### **Busy**

The CY7C056V and CY7C057V provide on-chip arbitration to resolve simultaneous memory location access (contention). If both ports' Chip Enables [3] are asserted and an address match occurs within  $t_{PS}$  of each other, the busy logic will determine which port has access. If  $t_{PS}$  is violated, one port will definitely gain permission to the location, but it is not predictable which port will get that permission. BUSY will be asserted  $t_{BLA}$  after an address match or  $t_{BLC}$  after  $\overline{CE}$  is taken LOW.

### Master/Slave

A  $M/\overline{S}$  pin is provided in order to expand the word <u>width</u> by configuring the device as either a master or a slave. The BUSY output of the master is connected to the BUSY input of the slave. This will allow the device to interface to a master device with no external components. Writing to slave devices must be delayed until after the BUSY input has settled ( $t_{BLC}$  or  $t_{BLA}$ ), otherwise, the slave chip may begin a write cycle during a contention situation. When tied HIGH, the  $M/\overline{S}$  pin allows the device to be used as a master and, therefore, the BUSY line is an output.  $\overline{BUSY}$  can then be used to send the arbitration outcome to a slave.

#### **Semaphore Operation**

The CY7C056V and CY7C057V provide eight semaphore latches, which are separate from the dual-port memory locations. Semaphores are used to reserve resources that are shared between the two ports. The state of the semaphore indicates that a resource is in use. For example, if the left port wants to request a given resource, it sets a latch by writing a zero to a semaphore location. The left port then verifies its success in setting the latch by reading it. After writing to the semaphore, SEM or OE must be deasserted for t<sub>SOP</sub> before attempting to read the semaphore. The semaphore value will be available  $t_{SWRD}$  +  $t_{DOE}$  after the rising edge of the semaphore write. If the left port was successful (reads a 0), it assumes control of the shared resource, otherwise (reads a 1) it assumes the right port has control and continues to poll the semaphore. When the right side has relinquished control of the semaphore (by writing a 1), the left side will succeed in gaining control of the semaphore. If the left side no longer requires the semaphore, a one is written to cancel its request.

Semaphores are accessed by asserting SEM LOW. The SEM pin functions as a chip select for the semaphore latches. For normal semaphore access,  $\mathsf{CE}^{[3]}$  must remain HIGH during SEM LOW. A  $\overline{\mathsf{CE}}$  active semaphore access is also available. The semaphore may be accessed through the right port with  $\overline{\mathsf{CE}}_{\mathsf{OR}}/\mathsf{CE}_{\mathsf{1R}}$  active by asserting the Bus Match Select (BM) pin LOW and asserting the Bus Size Select (SIZE) pin HIGH. The semaphore may be accessed through the left port with  $\overline{\mathsf{CE}}_{\mathsf{0L}}/\mathsf{CE}_{\mathsf{1L}}$  active by asserting all  $\overline{\mathsf{B}}_{\mathsf{0-3}}$  Byte Select pins HIGH.  $\mathsf{A}_{\mathsf{0-2}}$  represents the semaphore address.  $\overline{\mathsf{OE}}$  and  $\mathsf{R/W}$  are used in the same manner as a normal memory access. When writing or reading a semaphore, the other address pins have no effect.

When writing to the semaphore, only  $\rm I/O_0$  is used. If a zero is written to the left port of an available semaphore, a 1 will appear at the same semaphore address on the right port. That semaphore can now only be modified by the port showing 0 (the left port in this case). If the left port now relinquishes control by writing a 1 to the semaphore, the semaphore will be set to 1 for both ports. However, if the right port had requested the semaphore (written a 0) while the left port had control, the right port would immediately own the semaphore as soon as the left port released it. *Table 3* shows sample semaphore operations.

Table 1. Non-Contending Read/Write $^{[3]}$

|    |     | lr | nputs                                                            |     | Outputs                             |                                            |

|----|-----|----|------------------------------------------------------------------|-----|-------------------------------------|--------------------------------------------|

| CE | R/W | OE | $\overline{B}_0, \overline{B}_1, \overline{B}_2, \overline{B}_3$ | SEM | I/O <sub>0</sub> -I/O <sub>35</sub> | Operation                                  |

| Н  | Х   | Х  | X                                                                | Н   | High Z                              | Deselected: Power-Down                     |

| Х  | Х   | Х  | All H                                                            | Н   | High Z                              | Deselected: Power-Down                     |

| L  | L   | Χ  | H/L                                                              | Н   | Data In and High Z                  | Write to Selected Bytes Only               |

| L  | L   | Х  | All L                                                            | Н   | Data In                             | Write to All Bytes                         |

| L  | Н   | L  | H/L                                                              | Н   | Data Out and High Z                 | Read Selected Bytes Only                   |

| L  | Н   | L  | All L                                                            | Н   | Data Out                            | Read All Bytes                             |

| Х  | Χ   | Н  | Х                                                                | Х   | High Z                              | Outputs Disabled                           |

| Н  | Н   | L  | X                                                                | L   | Data Out                            | Read Data in Semaphore Flag                |

| Х  | Н   | L  | All H                                                            | L   | Data Out                            | Read Data in Semaphore Flag                |

| Н  |     | Х  | Х                                                                | L   | Data In                             | Write D <sub>IN0</sub> into Semaphore Flag |

| Х  |     | Х  | All H                                                            | L   | Data In                             | Write D <sub>IN0</sub> into Semaphore Flag |

| L  | Х   | Х  | Any L                                                            | L   |                                     | Not Allowed                                |

Table 2. Interrupt Operation Example (assumes  $\overline{\text{BUSY}}_{\text{L}} = \overline{\text{BUSY}}_{\text{R}} = \text{HIGH})^{[3, 44]}$

|                                   |                  | Left Port |    |                     |                   |                  | Right Port |                 |                     |                   |

|-----------------------------------|------------------|-----------|----|---------------------|-------------------|------------------|------------|-----------------|---------------------|-------------------|

| Function                          | R/W <sub>L</sub> | CE        | OE | A <sub>0L-13L</sub> | INT               | R/W <sub>R</sub> | CER        | OE <sub>R</sub> | A <sub>0R-13R</sub> | INT <sub>R</sub>  |

| Set Right INT <sub>R</sub> Flag   | L                | L         | Х  | 3FFF                | Х                 | Х                | Х          | Х               | Х                   | L <sup>[46]</sup> |

| Reset Right INT <sub>R</sub> Flag | Х                | Х         | Х  | Х                   | Х                 | Х                | L          | L               | 3FFF                | H <sup>[45]</sup> |

| Set Left INT <sub>L</sub> Flag    | Х                | Х         | Х  | Х                   | L <sup>[45]</sup> | L                | L          | Х               | 3FFE                | Х                 |

| Reset Left INT <sub>L</sub> Flag  | Х                | L         | L  | 3FFE                | H <sup>[46]</sup> | Х                | Х          | Х               | Х                   | Х                 |

**Table 3. Semaphore Operation Example**

| Function                            | I/O <sub>0</sub> -I/O <sub>8</sub> Left | I/O <sub>0</sub> -I/O <sub>8</sub> Right | Status                                                 |

|-------------------------------------|-----------------------------------------|------------------------------------------|--------------------------------------------------------|

| No Action                           | 1                                       | 1                                        | Semaphore Free                                         |

| Left Port Writes 0 to Semaphore     | 0                                       | 1                                        | Left Port Has Semaphore Token                          |

| Right Port Writes 0 to<br>Semaphore | 0                                       | 1                                        | No Change. Right Side Has No Write Access to Semaphore |

| Left Port Writes 1 to Semaphore     | 1                                       | 0                                        | Right Port Obtains Semaphore Token                     |

| Left Port Writes 0 to Semaphore     | 1                                       | 0                                        | No Change. Left Port Has No Write Access to Semaphore  |

| Right Port Writes 1 to<br>Semaphore | 0                                       | 1                                        | Left Port Obtains Semaphore Token                      |

| Left Port Writes 1 to Semaphore     | 1                                       | 1                                        | Semaphore Free                                         |

| Right Port Writes 0 to<br>Semaphore | 1                                       | 0                                        | Right Port Has Semaphore Token                         |

| Right Port Writes 1 to<br>Semaphore | 1                                       | 1                                        | Semaphore Free                                         |

| Left Port Writes 0 to Semaphore     | 0                                       | 1                                        | Left Port Has Semaphore Token                          |

| Left Port Writes 1 to Semaphore     | 1                                       | 1                                        | Semaphore Free                                         |

### Notes:

44. A<sub>0L-14L</sub> and A<sub>0R-14R</sub>, 7FFF/7FFE for the CY7C057V.

45. If BUSY<sub>R</sub>=L, then no change.

46. If BUSY<sub>L</sub>=L, then no change.

### Right Port Configuration [47, 48, 49]

| ВМ | SIZE | Configuration            | I/O Pins Used       |

|----|------|--------------------------|---------------------|

| 0  | 0    | x36 (Standard)           | I/O <sub>0-35</sub> |

| 0  | 1    | x36 (CE Active SEM Mode) | I/O <sub>0-35</sub> |

| 1  | 0    | x18                      | I/O <sub>0-17</sub> |

| 1  | 1    | х9                       | I/O <sub>0-8</sub>  |

### **Right Port Operation**

| Configuration | WA | ВА | Data Accessed <sup>[50]</sup> | I/O Pins Used       |

|---------------|----|----|-------------------------------|---------------------|

| x36           | Х  | Х  | DQ <sub>0-35</sub>            | I/O <sub>0-35</sub> |

| x18           | 0  | Х  | DQ <sub>0-17</sub>            | I/O <sub>0-17</sub> |

| x18           | 1  | X  | DQ <sub>18-35</sub>           | I/O <sub>0-17</sub> |

| х9            | 0  | 0  | DQ <sub>0-8</sub>             | I/O <sub>0-8</sub>  |

| х9            | 0  | 1  | DQ <sub>9-17</sub>            | I/O <sub>0-8</sub>  |

| х9            | 1  | 0  | DQ <sub>18-26</sub>           | I/O <sub>0-8</sub>  |

| х9            | 1  | 1  | DQ <sub>27-35</sub>           | I/O <sub>0-8</sub>  |

### **Left Port Operation**

| Control Pin | Effect                            |

|-------------|-----------------------------------|

| BO          | I/O <sub>0-8</sub> Byte Control   |

| B1          | I/O <sub>9-17</sub> Byte Control  |

| B2          | I/O <sub>18-26</sub> Byte Control |

| B3          | I/O <sub>27–35</sub> Byte Control |

#### Notes:

- 47. BM and SIZE must be configured one clock cycle before operation is guaranteed.

- In x36 mode WA and BA pins are "Don't Ćare." In x18 mode BA pin is a "Don't Care."

- DQ represents data output of the chip.

When reading a semaphore, data lines 0 through 8 output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within t<sub>SPS</sub> of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.

When reading a semaphore, data lines 0 through 8 output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the

semaphore within t<sub>SPS</sub> of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.

When reading a semaphore, data lines 0 through 8 output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within t<sub>SPS</sub> of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.

### **Bus Match Operation**

The right port of the CY7C057V 32Kx36 dual-port SRAM can be configured in a 36-bit long-word, 18-bit word, or 9-bit byte format for data I/O. The data lines are divided into four lanes, each consisting of 9 bits (byte-size data lines).

The Bus Match Select (BM) pin works with Bus Size Select (SIZE) to select bus width (long-word, word, or byte) for the right port of the dual-port device. The data sequencing arrangement is selected using the Word Address (WA) and Byte Address (BA) input pins. A logic "0" applied to both the Bus Match Select (BM) pin and to the Bus Size Select (SIZE) pin will select long-word (36-bit) operation. A logic "1" level applied to the Bus Match Select (BM) pin will enable either byte or word bus width operation on the right port I/Os depending on the logic level applied to the SIZE pin. The level of Bus Match Select (BM) must be static throughout device operation.

Normally, the Bus Size Select (SIZE) pin would have no standard-cycle application when BM = LOW and the device is in long-word (36-bit) operation. A "special" mode has been added however to disable ALL right port I/Os while the chip is active. This I/O disable mode is implemented when SIZE is forced to a logic "1" while BM is at a logic "0". It allows the busmatched port to support a chip enable "Don't Care" semaphore read/write access similar to that provided on the left port of the device when all Byte Select  $(\overline{B}_{0-3})$  control inputs are deselected.

The Bus Size Select (SIZE) pin selects either a byte or word data arrangement on the right port when the Bus Match Select (BM) pin is HIGH. A logic "1" on the SIZE pin when the BM pin is HIGH selects a byte bus (9-bit) data arrangement). A logic "0" on the SIZE pin when the BM pin is HIGH selects a word bus (18-bit) data arrangement. The level of the Bus Size Select (SIZE) must also be static throughout normal device operation.

#### Long-Word (36-bit) Operation

Bus Match Select (BM) and Bus Size Select (SIZE) set to a logic "0" will enable standard cycle long-word (36-bit) operation. In this mode, the right port's I/O operates essentially in an identical fashion as does the left port of the dual-port SRAM. However no Byte Select control is available. All 36 bits of the long-word are shifted into and out of the right port's I/O buffer stages. All read and write timing parameters may be identical with respect to the two data ports. When the right port is configured for a long-word size, Word Address (WA), and Byte Address (BA) pins have no application and their inputs are "Don't Care" [51] for the external user.

#### Word (18-bit) Operation

Word (18-bit) bus sizing operation is enabled when Bus Match Select (BM) is set to a logic "1" and the Bus SIze Select (SIZE) pin is set to a logic "0." In this mode, 18 bits of data are ported through  $\rm I/O_{0R-17R}$ . The level applied to the Word Address (WA) pin during word bus size operation determines whether the most-significant or least-significant data bits are ported through the  $\rm I/O_{0R-17R}$  pins in an Upper Word/Lower Word select fashion (note that when the right port is configured for word size operation, the Byte Address pin has no application and its input is "Don't Care"  $\rm [51]$ ).

Device operation is accomplished by treating the WA pin as an additional address input and using standard cycle address and data setup/hold times. When transferring data in word (18-bit) bus match format, the unused  $I/O_{18R-35R}$  pins are three-stated.

#### Byte (9-bit) Operation

Byte (9-bit) bus sizing operation is enabled when Bus Match Select (BM) is set to a logic "1" and the Bus Size Select (SIZE) pin is set to a logic "1." In this mode, data is ported through  $I/O_{0R-8R}$  in four groups of 9-bit bytes. A particular 9-bit byte group is selected according to the levels applied to the Word Address (WA) and Byte Address (BA) input pins.

| I/Os                   | Rank      | WA | BA |

|------------------------|-----------|----|----|

| I/O <sub>27R-35R</sub> | Upper-MSB | 1  | 1  |

| I/O <sub>18R-26R</sub> | Lower-MSB | 1  | 0  |

| I/O <sub>9R-17R</sub>  | Upper-MSB | 0  | 1  |

| I/O <sub>0R-8R</sub>   | Lower-MSB | 0  | 0  |

Device operation is accomplished by treating the Word Address (WA) pin and the Byte Address (BA) pins as additional address inputs having standard cycle address and data set-up/hold times. When transferring data in byte (9-bit) bus match format, the unused  $I/O_{9R-35R}$  pins are three-stated.

#### Note

51. Even though a logic level applied to a "Don't Care" input will not change the logical operation of the dual-port, inputs that are temporarily a "Don't Care" (along with unused inputs) must not be allowed to float. They must be forced either HIGH or LOW.

### **Ordering Information**

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package Type                   | Operating<br>Range |

|---------------|----------------|-----------------|--------------------------------|--------------------|

| 12            | CY7C056V-12AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C056V-12BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

| 15            | CY7C056V-15AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C056V-15BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

| 20            | CY7C056V-20AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C056V-20BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package Type                   | Operating<br>Range |

|---------------|----------------|-----------------|--------------------------------|--------------------|

| 12            | CY7C057V-12AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C057V-12BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

| 15            | CY7C057V-15AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C057V-15AI  | A144            | 144-Pin Thin Quad Flat Pack    | Industrial         |

|               | CY7C057V-15BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

|               | CY7C057V-15BBI | BB172           | 172-Ball Ball Grid Array (BGA) | Industrial         |

| 20            | CY7C057V-20AC  | A144            | 144-Pin Thin Quad Flat Pack    | Commercial         |

|               | CY7C057V-20BBC | BB172           | 172-Ball Ball Grid Array (BGA) | Commercial         |

### **Package Diagrams**

### 144-Pin Plastic Thin Quad Flat Pack (TQFP) A144

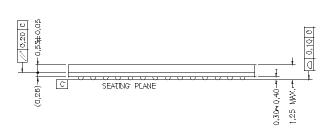

### Package Diagrams (continued)

### 172-Ball BGA BB172

|      | Document Title: CY7C056V/CY7C057V 3.3V 16K/32K x 36 FLEx36™ Asynchronous Dual-Port Static RAM Document Number: 38-06055 |               |                    |                                               |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|-----------------------------------------------|--|--|--|--|

| REV. | ECN NO.                                                                                                                 | Issue<br>Date | Orig. of<br>Change | Description of Change                         |  |  |  |  |

| **   | 110214                                                                                                                  | 12/16/01      | SZV                | Change from Spec number: 38-00742 to 38-06055 |  |  |  |  |